- Главная

- /

- Технология

- /

- Цифра

Джиттер и борьба с ним

Слуховые ограничения и принципы компрессии аудиоданных

Несмотря на то, что джиттер является общеизвестным артефактом цифрового аудио, его влияние на реальное звучание зачастую недооценивается. Влияние джиттера может быть особенно ощутимым в больших вещательных и студийных комплексах, где используются длинные соединительные кабели и имеет место несогласованность нагрузок. Появление преобразователей нового поколения, отличающихся очень малым внутренним джиттером и широкими возможностями его снижения, позволило применять в вещательной отрасли высокоскоростные коаксиальные интерфейсы, которыми можно заменить широко распространенные кабели типа "витая пара". Это позволяет уменьшить уровень джиттера, обусловленного особенностями интерфейса.

Природа джиттера

Джиттер в цифровых звуковых интерфейсах может возникать в источнике сигнала или генерироваться самим интерфейсом. Нестабильность тактовых импульсов (clock jitter), вызванная генерированием сигнала AES/EBU, может стать началом снижения разрешения, но главной причиной появления джиттера и возрастания его значения до критичного уровня является ограничение полосы пропускания самого интерфейса. Причем это проявляется именно там, где особенно нежелательно – при преобразовании цифрового сигнала в аналоговый. Зачастую ускользает от внимания тот факт, что преобразователи частоты дискретизации тоже порождают интерфейсный джиттер – несмотря на то, что эти преобразователи могут иметь очень малую нестабильность тактовой частоты, они все равно наносят ущерб сигналу при преобразовании. Передискретизированные звуковые данные с искаженной информацией синхронизации приводят к появлению ошибки в реконструированном потоке данных. Нестабильность тактовой частоты будет малой, но форма аналогового сигнала исказится. Анализатор джиттера при исследовании интерфейсного джиттера не позволяет определить, какой формы должен быть аналоговый сигнал. Таким образом, малый уровень джиттера после преобразования частоты дискретизации не является гарантией сохранения качества сигнала.

Рассмотрим практические примеры того, какое воздействие оказывает стандартная витая пара на процесс аналогово-цифрового преобразования, и как двойная схема ФАПЧ (фазовой автоподстройки частоты) с малым джиттером позволяет корректировать его. Ряд диаграмм, построенных анализатором джиттера высокого разрешения, применявшимся при проведении исследований, показывает, как искажения, вызванные джиттером данных и интерфейсным джиттером, сказываются на качестве сигнала и как они обрабатываются стандартными схемами одинарной системы ФАПЧ. Джиттер в ЦАП может при воссоздании аналогового сигнала привести к снижению разрешения до уровней, когда искажения становятся хорошо слышными. Это демонстрирует тот вред, который наносит джиттер целостной и прозрачной работе системы.

Нестабильность тактовой частоты (clock jitter)

Джиттер, который приводит к потере разрешения и искажениям воссозданного аналогового сигнала, называется нестабильностью тактовой частоты (clock jitter). Эта нестабильность тактовой частоты присутствует в сигналах синхронизации word clock или master clock, генерируемых микросхемой ЦАП. Измеряемый на этом этапе джиттер представляет собой отклонение от частоты синхронизации при преобразовании от идеального тактового сигнала.

Эти отклонения частоты делятся на джиттер по частоте и джиттер по амплитуде. Визуализированная картина исследований этих сигналов с помощью осциллографа дает представление о максимальных значениях (от пика до пика), но не предоставляет никакой информации о частоте джиттера. Использование осциллографа для исследования джиттера длительностью менее 1 наносекунды является практически невозможным, поэтому необходим специальный анализатор джиттера. Устройство, которое применялось в исследованиях, характеризуется значением собственного джиттера 0,4 пикосекунды (в среднеквадратичном значении) для тактовой частоты 12,288 МГц (то есть 256-кратная передискретизация от частоты 48 кГц) и 1,2 пс для 192 кГц (4-кратная передискретизация от частоты 48 кГц).

Таблица 1. Максимальный джиттер для различных значений разрешения

|

Джиттер, пс |

8 |

16 |

32 |

64 |

128 |

256 |

512 |

1024 |

2048 |

4096 |

|

Разрядность, бит |

20 |

19 |

18 |

17 |

16 |

15 |

14 |

13 |

12 |

11 |

Теоретическая деградация для высоких частот (более 5 кГц) приведена в таблице 1. Эта таблица ничего не говорит о том, насколько слышны искажения, вызванные джиттером. Она лишь содержит измеренные искажения, обусловленные влиянием джиттера на дискретные частоты.

Если посмотреть на возрастание шумового уровня, то станут видны значения, показанные в таблице 2.

Таблица 2. Максимальный джиттер для различных уровней шума

|

Джиттер, пс |

1 |

2 |

3 |

4 |

16 |

|

Уровень шума, дБ |

-105 |

-97 |

-90 |

-84 |

-79 |

Высокочастотный джиттер приводит к более слышимой деградации, чем низкочастотный. Высокочастотные сигналы также больше страдают от джиттера определенного уровня, чем низкочастотные.

Интерфейсный джиттер

Интерфейсный джиттер, вероятно, вносит наибольшую лепту в общий уровень джиттера всей системы. В частности, ограничения полосы пропускания соединений цифрового звука, выполненных кабелем типа "витая пара", могут вызвать серьезное понижение общей эффективности цифро-аналогового преобразователя. В силу ограничений по полосе пропускания, присущих интерфейсному кабелю, и в результате изменения формы сигнала AES/EBU появляется значительная деградация сигнала синхронизации в наиболее распространенных микросхемах приемников. Наиболее часто применяемые микросхемы CS8412 и CS8414 фирмы Crystal характеризуются частотой понижения джиттера 25 кГц. Это частота, на которой встроенная схема ФАПЧ начинает понижать джиттер входного сигнала. Если иметь в виду, что частота джиттера любого происхождения может достигать 40 кГц, то можно сделать заключение, что возможностей этих микросхем в плане снижения джиттера явно недостаточно. Большим преимуществом этих микросхем является способность надежно привязываться к сигналам с высоким джиттером различной амплитуды и продолжать непрерывно работать. Это является ключевым условием надежной работы любого цифро-аналогового преобразователя.

Топология системы с двойной ФАПЧ

Для реализации надежного восстановления данных и снижения джиттера требуется подход, предусматривающий двойную обработку. Если схема способна делать корректно что-то одно, она, как правило, не способна с такой же высокой точностью выполнять какую-либо другую задачу.

Поэтому появилась концепция использования топологии с двойной ФАПЧ. Входные цепи на основе уже упоминавшейся микросхемы CS8414 в сочетании с преобразователем тактовой частоты с большой пропускной способностью позволяют обеспечить точное и надежное восстановление данных. На следующем этапе применяется схема дискретной ФАПЧ на базе специально разработанных микросхем VCXO. На один канал используются две такие микросхемы, обеспечивая декодирование четырех наиболее распространенных тактовых частот: 44,1 и 88,2 кГц декодируются первой VCXO, а 48 и 96 кГц – второй. (Частота 32 кГц также принимается устройством, но к ней не применяется процедура снижения джиттера). Новый фазовый компаратор используется для реализации механизма привязки к сигналу синхронизации без так называемых "мертвых зон", имеющих место при применении ряда других фазовых компараторов и схем ФАПЧ. Это также позволяет снизить уровень собственного джиттера.

Собственный джиттер и понижение джиттера

Важной характеристикой высокопроизводительного звукового цифро-аналогового преобразователя является собственный джиттер устройства при подключении источника сигнала, свободного от джиттера. Микросхема CS 8414 имеет собственный джиттер примерно 150 пс в среднеквадратичном значении.

Чтобы обеспечить полное использование разрешения микросхем 24-разрядного ЦАП, вторая схема ФАПЧ имеет собственный джиттер всего 2 пс в среднеквадратичном значении. В сочетании с частотой понижения джиттера 25 кГц и возможностью подавления джиттера более чем на 60 дБ конвертер может работать с входными сигналами с очень высоким значением джиттера без ухудшения общей производительности системы.

Деградация производительности системы

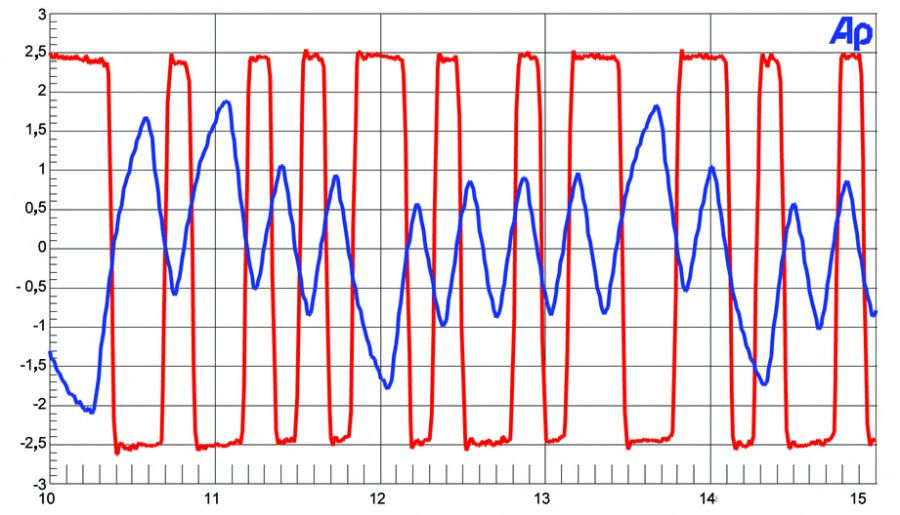

Если посмотреть на тестовый сигнал стандартного потока данных AES/EBU на выходе нормального кабеля AES/EBU длиной 100 м, то деградация сигнала при использовании одинарной схемы ФАПЧ становится очевидной. На рисунке 1 можно видеть осциллограмму сигнала AES/EBU, снятую до и после его прохождения по стометровому кабелю.

Рис.1. Сигнал AES/EBU до (красный) и после (синий) прохождения по кабелю типа "витая пара" длиной 100 м

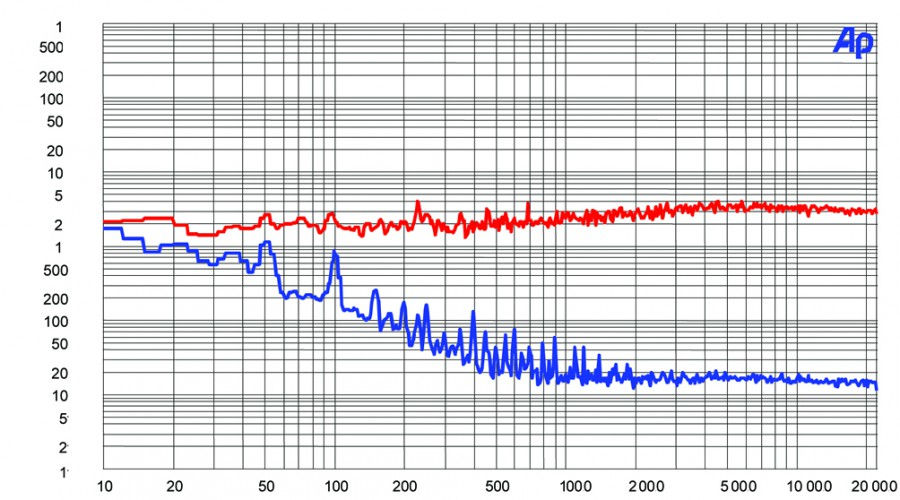

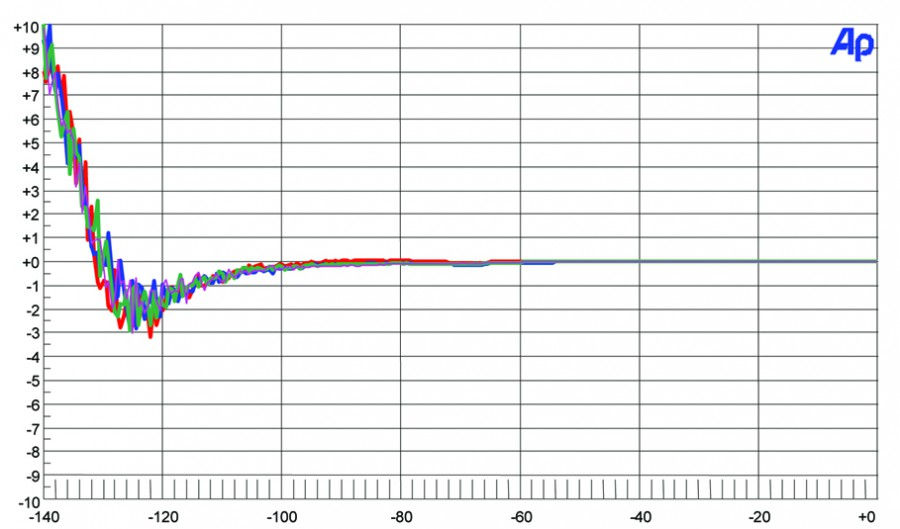

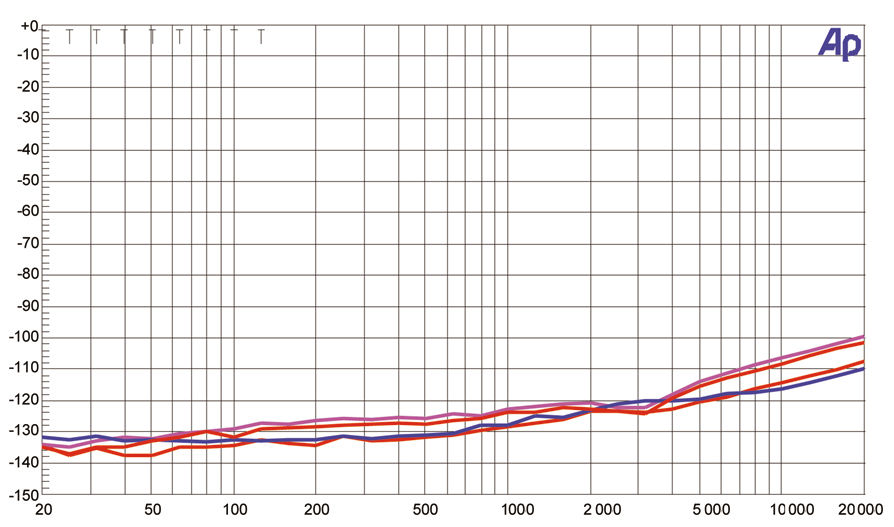

На рисунке 2 показан собственный джиттер первой и второй цепей ФАПЧ преобразователя ADA-524.

Рис. 2. Собственный джиттер ADA-524 после первой (красный) и второй (синий) схемы ФАПЧ. Среднеквадратичные значения вычислены для 150 и 2 пс соответственно. Примечание: 1нс = 10-9 с; 1пс = 10-12 с; 1фс = 10-15 с

Рисунок 3 показывает результат применения симулятора кабеля длиной 100 м и изменение уровня джиттера, вызванное ограничением частоты из-за явления низкочастотной фильтрации кабеля.

Рис. 3. Джиттер ADA-524 после первой (красный) и второй (синий) схемы ФАПЧ при использовании 100-м кабельного симулятора. Среднеквадратичные значения вычислены для 2,7 нс и 35 пс соответственно

Увеличение джиттера очевидно, как и функция его понижения при помощи второй цепи ФАПЧ. Работа этой цепи начинает снижать джиттер на частоте 25 кГц и резко понижает джиттер до незначительного уровня. Собственный уровень джиттера снижается до такого малого значения, как 0,05 пс.

Все это, разумеется, хорошо, но что происходит с реальным аналоговым сигналом и как понижается его качество под воздействием интерфейсного джиттера?

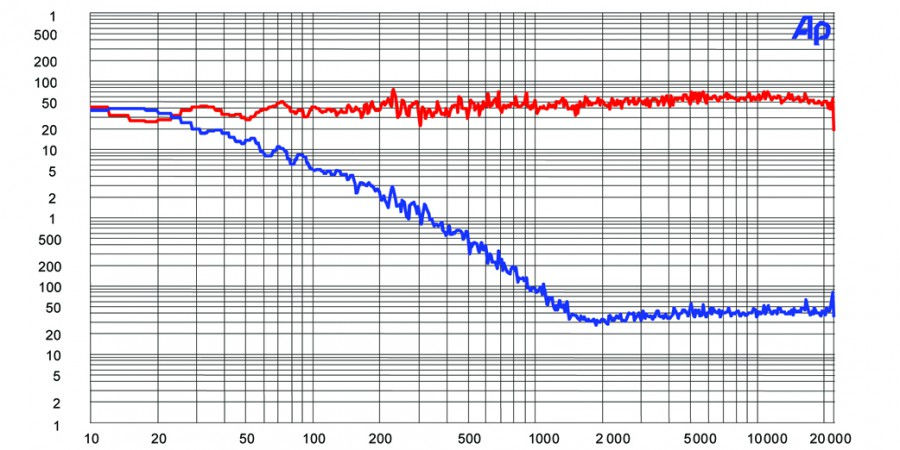

На рисунке 4 приведены диаграммы, на которых показан параметр THD+N (Total Harmonic Distortion + Noise – общие нелинейные искажения + шум) в зависимости от частоты. Снижение качества работы системы в отсутствие второй цепи ФАПЧ очевидно.

Рис. 4. Зависимость THD+N от частоты, сверху вниз (возбудитель – 7 кГц):

красный – 100-м кабельный симулятор и одна схема ФАПЧ (CS8414);

зеленый – одна схема ФАПЧ без кабельного симулятора;

синий – двойная ФАПЧ с кабельным симулятором;

фиолетовый – двойная ФАПЧ без кабельного симулятора

Рисунок показывает, насколько эффективно топология с двойной ФАПЧ позволяет работать с деградировавшим входным сигналом, для которого параметр THD+N достигает -75 дБ. Здесь роль играют не только нелинейные искажения, но и, в основном, шум. Высокий уровень шума снижает эффективное разрешение конвертера. Следует обратить внимание, что две нижние кривые практически идентичны, то есть разрешение системы восстановлено.

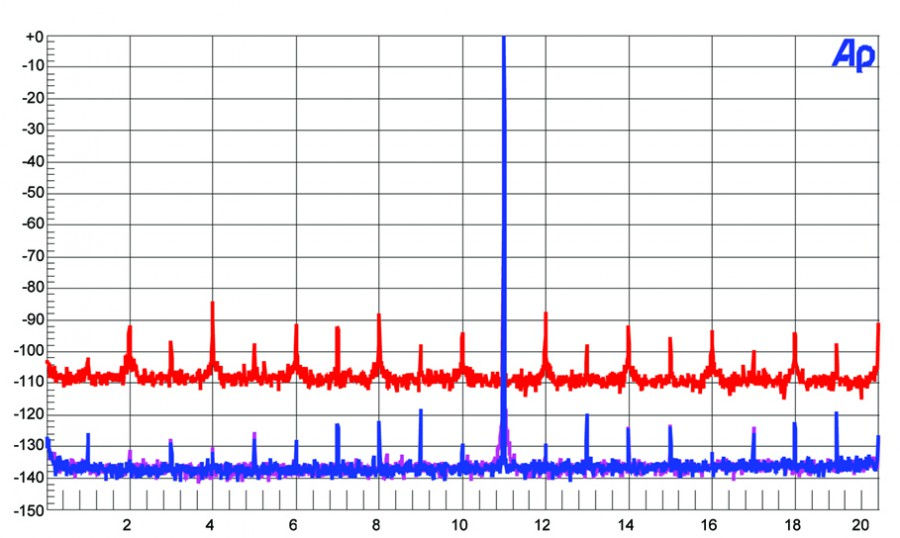

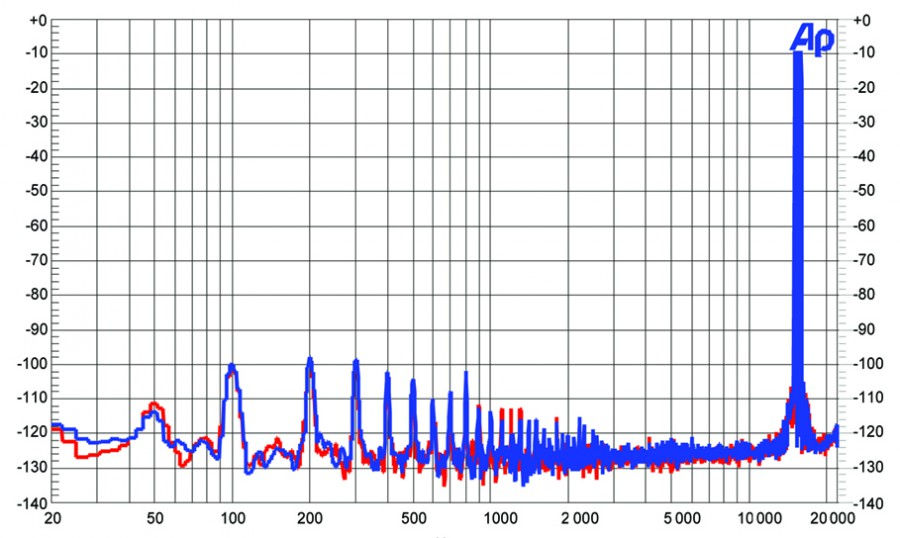

Кривая, полученная на основе быстрого преобразования Фурье, примененного к сигналу частотой 11 кГц с кабельным симулятором и без него, показана на рисунке 5. На рисунке четко видно повышение уровня шума. Чтобы это было видно лучше, гармоники удалены из этого графика.

Рис. 5. Зависимость THD+N от частоты, сверху вниз (возбудитель – 11 кГц):

красный – 100-м кабельный симулятор и только одна схема ФАПЧ (CS8414);

фиолетовый – одна схема ФАПЧ без кабельного симулятора;

синий – двойная ФАПЧ с кабельным симулятором

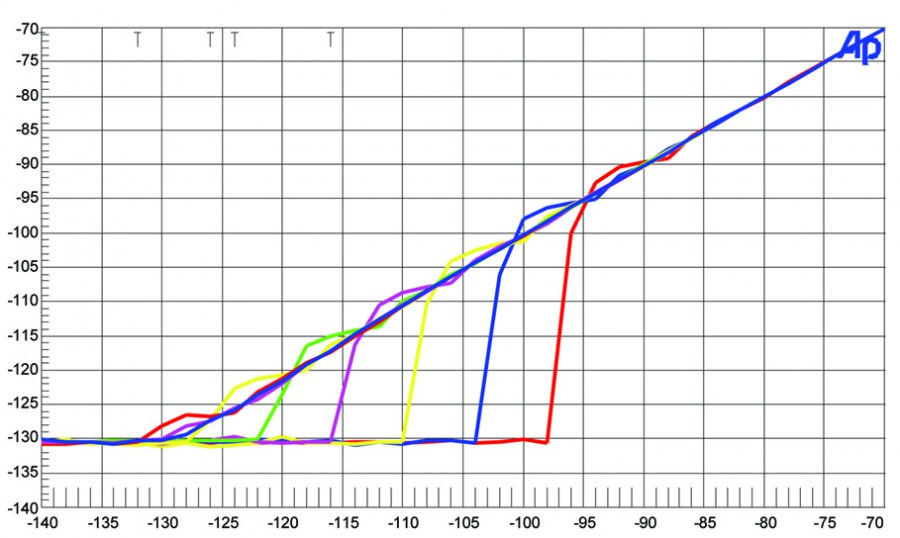

Эффективность системы

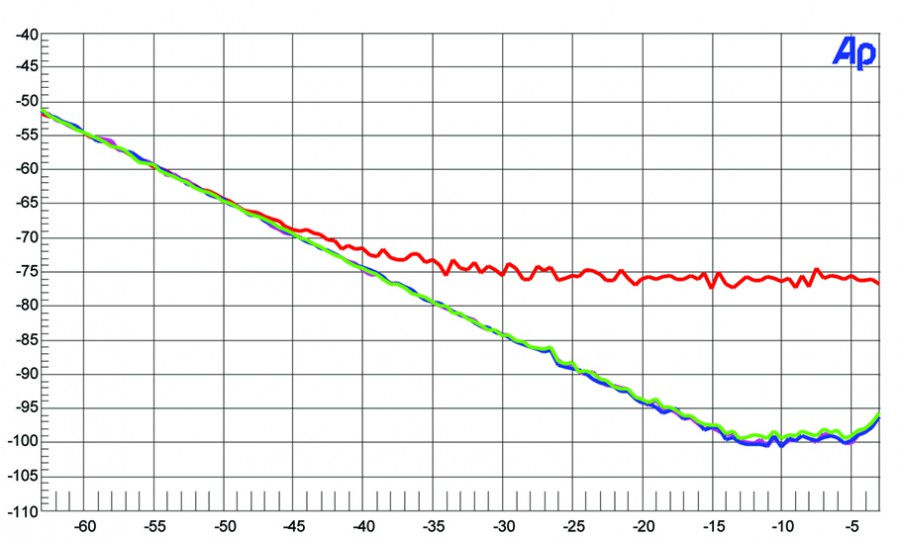

Линейная диаграмма на рисунке 6 еще лучше демонстрирует эффективность технологии.

Рис. 6. Диаграмма линейности (с уходом в шум)

Кривая показывает отклонение параметров используемой микросхемы ЦАП в сравнении с параметрами идеальной микросхемы, диаграмма которых представляет собой идеальную горизонтальную прямую. Ошибка величиной 3 дБ появляется на -132 дБ, что эквивалентно 22-битному разрешению. На рисунке 7 показана линейность устройства при подаче на него 16...24-разрядных данных длиной в одно слово.

Рис. 7. Диаграмма линейности, справа налево: длина входного слова составляет 16, 17, 18, 19, 20, 21, 22, 23 и 24 бита

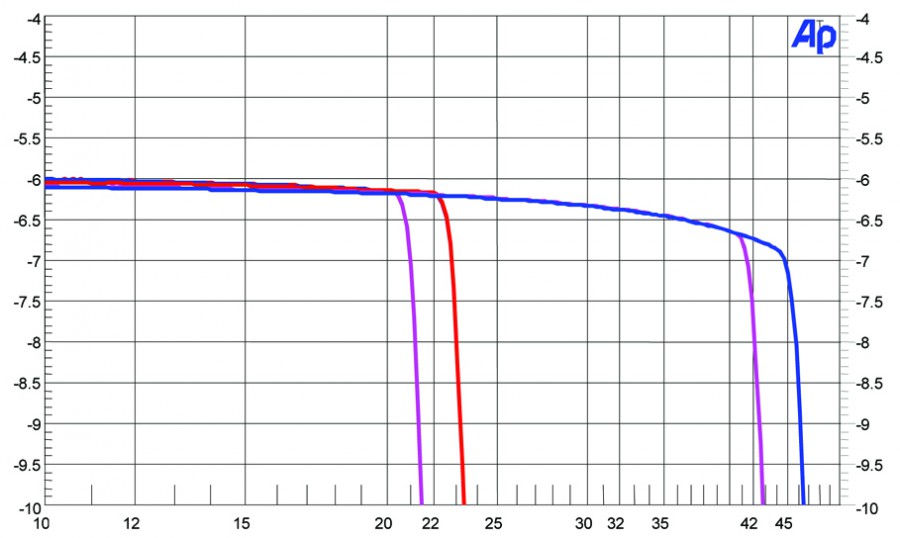

АЧХ ЦАП, преобразующего цифровой сигнал с частотой дискретизации 96 кГц, показана на рисунке 8.

Рис. 8. АЧХ для сигнала уровня -6 дБ с частотами дискретизации 44,1; 48; 88,2 и 96 кГц

Диаграммы перекрестных помех приведены на рисунке 9.

Рис. 9. Перекрестные помехи

Для выявления интермодуляционных искажений использовался сигнал, формирующий на частоте 100 Гц несколько интермодуляционных составляющих с различными частотами. Результат испытаний показан на рисунке 10.

Рис. 10. Интермодуляционные составляющие при мультитональных сигналах с частотами 15 – 15,2 – 15,3 – 15,5 – 15,6 – 15,7 – 15,8 – 16 кГц

Заключение

Тестирование качества звука цифро-аналогового конвертера при помощи статичных сигналов полезно лишь в том случае, когда соединительные линии имеют небольшую длину, а источники цифрового сигнала имеют очень малый уровень джиттера, что в реальности случается очень редко. Использование коаксиальных соединений с волновым сопротивлением 75 Ом позволяет уменьшить деградацию производительности системы по сравнению с витой парой. Если есть необходимость в цифро-аналоговом преобразовании, применение на входе схемы с двойной ФАПЧ (не любой, а высококачественной) позволяет существенно снизить уровень деградации сигнала.

09 сентября 2015

Питер Скут

Пока никто еще не оставлял комментарии. Вы можете быть первым.

Возможность оставлять комментарии доступна только для зарегистрированных пользователей.